芯片和硬件設計因其復雜性和先進的技術而面臨眾多挑戰。這些挑戰導致在合成、驗證、物理設計和可靠性循環期間優化性能、功耗、面積和成本(PPAC)的周轉時間(TAT)更長。

大語言模型(LLMs)已顯示出大規模理解和生成自然語言的出色能力,從而為各種領域帶來許多潛在應用和優勢。成功地將基于 LLMs 的 AI 智能體用于硬件設計,可以大幅減少 TAT,從而縮短產品周期、降低成本、提高設計可靠性,并降低代價高昂的錯誤風險。

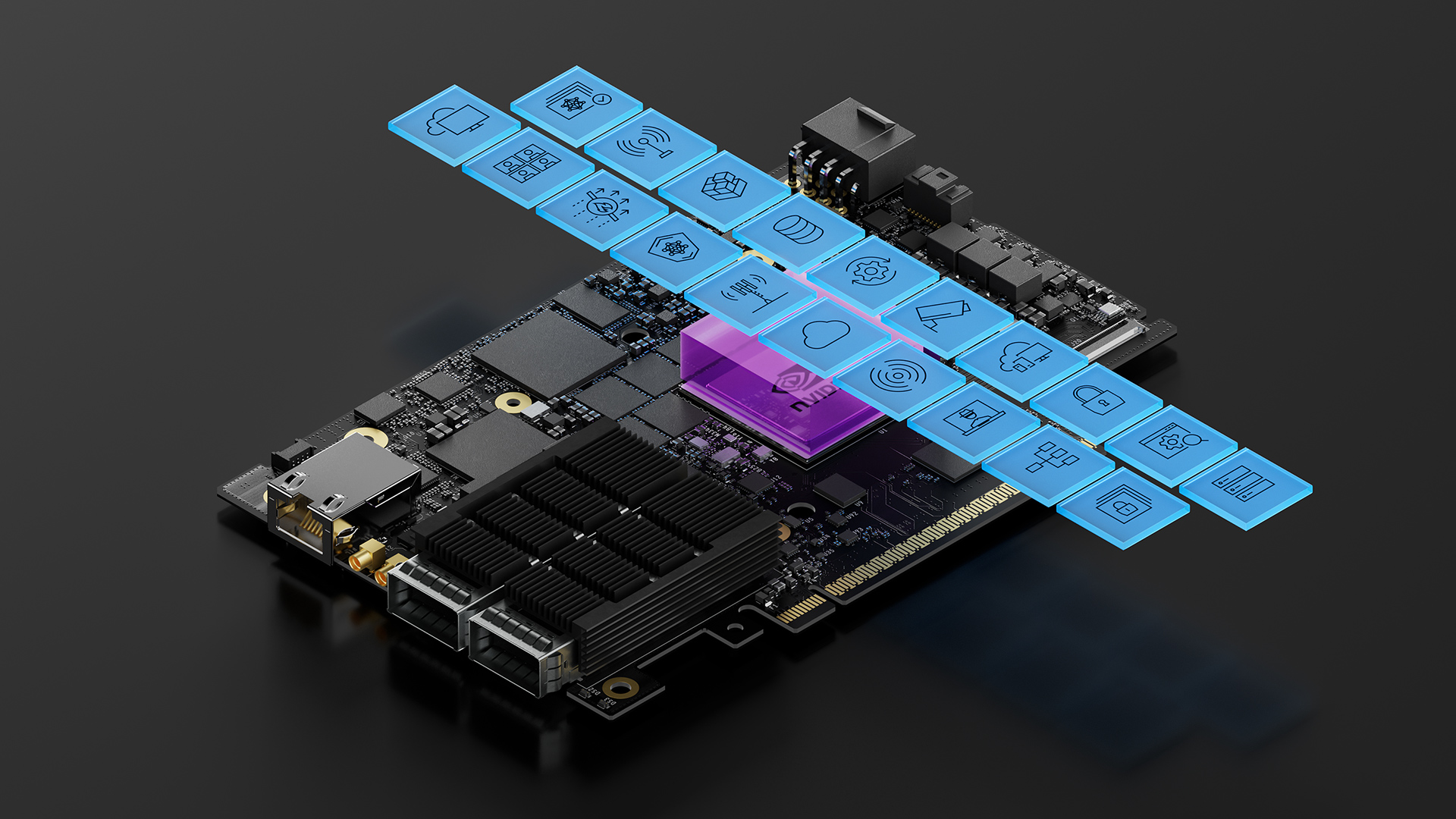

圖 1. Marco 框架概述

Marco:基于圖形的可配置任務求解和多 AI 代理框架

我們介紹了擬議的 Marco 框架,其中包括基于圖形的任務求解、子任務的智能體配置,以及每個 AI 智能體的實時技能/工具配置。

圖 1 展示了基于動態和靜態可配置圖形的任務求解,可靈活集成芯片設計知識 (例如電路、定時等)。

在任務圖中,每個節點代表一個子任務,每個邊緣代表節點之間的執行或知識關系。為了解決每個子任務,您可以使用 Autogen 配置具有知識數據庫、工具和內存的單個 AI 或多個 AI 代理。

表 1 總結了各種代理的 Marco 框架的任務圖形、代理和 LLM 配置。 VerilogCoder 和 MCMM 時序分析代理使用動態任務圖形分別完成對 RTL 的規范和提取時序報告的關鍵要點。定時路徑調試代理通過靜態定時調試任務圖 (圖 1) 查找有問題的網絡、線和約束。

| 代理作品 | 任務類別 | Marco 框架配置 | ||

| 任務圖 | 子任務代理配置。 | 定制工具 | ||

| RTLFixer | 代碼語法固定 | 不適用 | 單 AI | RTL 語法錯誤 RAG 數據庫 |

| Standard Cell Layout Opt. | 優化 | 不適用 | 單 AI | Cluster Evaluator, Netlist Traverse Tool |

| MCMM 定時分析 (Partition/Block-Level) | 總結和異常識別 | 動態 | 多 AI | Timing Distribution Calculator,Timing Metric Comparator |

| DRC Coder | 代碼生成 | 不適用 | 多模態和多 AI | Foundry Rule Analysis,Foundry 規則分析,Layout DRV Analysis,布局 DRV 分析,DRC Code Evaluation,DRC 代碼評估 |

| Timing Path Debug(Path-Level) | 總結和異常識別 | 靜態 | 分層多 AI | 代理定時報告檢索 |

| VerilogCoder | 代碼生成 | 動態 | 多 AI | TCRG 檢索工具,AST-Based Waveform Tracing Tool |

表 1、任務圖、代理配置、Marco 框架的定制工具,用于硬件設計任務的各種自主代理實現

在表 1 中,使用 Marco 框架支持 RTLFixer 和標準單元布局優化代理 (即單 AI 配置)。其余的多 AI 代理均在 Marco 框架上實施。

對于 RTLFixer、用于標準單元布局優化的 LLM 代理和 DRC Coder,我們使用了具有定制工具、內存和域知識的單 AI 或多 AI 代理配置。

自動硬件描述語言代碼生成

自主智能體產生影響的一個關鍵領域是硬件描述語言(HDL)的生成,例如 Verilog。由于 VLSI 設計的復雜性與日俱增,編寫 Verilog 和 VHDL 非常耗時且容易出現錯誤,因此需要進行多次迭代來調試功能正確性。因此,降低設計成本和設計師完成硬件規格的工作量已成為一項迫切需求。

LLM 可用于根據自然語言描述生成 Verilog 代碼。但是,LLM 通常難以生成語法和功能上都正確的代碼。

語法正確性

RTLFixer 結合使用檢索增強生成 (RAG) 和 ReAct 提示,使 LLM 能夠迭代地調試和修復語法錯誤。RAG 整合了人類專家指導數據庫,為糾錯提供上下文。ReAct 啟用 LLM 進行錯誤推理、計劃修復并采取行動。

功能正確性

VerilogCoder 是一個多代理系統,包含任務規劃器和基于抽象語法樹(AST)-based 波形追蹤工具,用于生成和調試 Verilog 代碼。它使用任務和電路關系圖(TCRG)將任務分解為可管理的子任務,并將信號轉換鏈接到每個步驟(圖 2)。

圖 2、任務驅動的電路關系圖檢索代理推理,并與開發的 TCRG 檢索工具交互,通過相關的電路和信號描述豐富任務

基于 AST 的波形追蹤工具通過回溯信號波形來協助 LLM 代理識別和修復功能錯誤。與之前的方法相比,VerilogCoder 在 VerilogEval-Human v2 基準測試中的成功率為 94.2%。

在視頻 1 中,VerilogCoder 演示使用 TCRG 規劃和基于 AST 的波形追蹤工具自動完成功能正確的 Verilog 代碼。

自動生成 DRC 布局代碼

DRC-Coder 使用多個具有視覺功能的自主代理以及專門的 DRC 和布局 DRV 分析工具來生成 DRC 代碼。該系統從文本描述、視覺插圖和布局表示中解釋設計規則。多個 LLM 代理包括一個解釋設計規則的規劃器和一個將規則轉換為可執行代碼的程序員。

DRC-Coder 包含自動調試流程,該流程利用代碼評估的反饋來優化生成的代碼。

視頻 2、用于芯片設計的 DRC-Coder 演示

在視頻 2 中,DRC-Coder 演示會生成 DRC 代碼,通過利用布局分析工具、自動調試流程以及多模態和多 AI 代理的功能,在數百個測試布局中實現完美的 F1 分數。

DRC-Coder 在為低于 3nm 的技術節點生成 DRC 代碼時,達到了完美的 F1 評分 (達到 1.000 分),優于標準提示技術。擬議的自動化代理方法可顯著縮短 DRC 代碼生成所需的時間,即每個設計規則從數周縮短到平均 4 分鐘。

標準單元布局優化

用于標準單元布局優化的 LLM 智能體建議使用 LLM 的自然語言和推理能力逐步生成高質量集群約束,以優化單元布局 PPA,并使用 ReAct 提示調試可路由性。

該系統使用網絡信息和單元布局分析將 MOSFET 設備分組到集群中。與在工業 2nm 技術節點中的一組順序單元上采用基于 Transformer 的設備集群方法相比,AI 智能體不僅可將單元面積減少多達 19.4%,而且還可生成多 23.5% 的 LVS 和 DRC 清潔單元布局。

多角度多模式時序報告調試與分析

多角多模 (MCMM) 時序分析代理使用動態任務圖形分別完成從規范到 RTL 的規范,并提取時序報告的關鍵要點。

根據經驗豐富的工程師對一組工業案例的評估,MCMM 時序分析代理的平均分為 8.33 分 (滿分 10 分),與人類工程師相比,速度提高了約 60 倍 (圖 3)。

圖 3、MCMM 時序分析代理結果

定時路徑調試代理通過靜態定時調試任務圖 (圖 1) 查找有問題的 net、wire 和約束。

在表 2 中,定時路徑調試代理可解析 86% 的路徑級調試任務,而標準任務求解方法無法解析任何任務。

| 多報告任務說明 | 所需的分析結果 子任務 | 標準任務求解 | 定時路徑調試代理 |

| 查找沒有上升/下降信息的缺失 clk 信號 | max、clk | X | V |

| 識別 nets 對的 RC 不匹配率高 | Max、Wire | X | V |

| 檢測受害者與侵犯者之間的異常約束 | Max、xtalk、LC | X | V |

| 識別犧牲者與侵犯者之間的異常 RC 值 | Max、wire、xtalk、LC | X | V |

| 查找具有最高 RC 值的最慢階段的限制 | Max、wire、xtalk、LC | X | V |

| 比較每個 timing table,了解階段數、點值和 timing mismatch | 最大值 | X | X |

| 任務 M2 和任務 M3,用于路徑列表中的特定階段 | Max、wire、xtalk、LC | X | V |

| 平均通過率 | 0% | 86% | |

表 2、具有靜態任務圖求解功能的定時路徑調試代理的通過率 (%),以及無任務圖信息的樸素標準任務求解

X = 無法解決任務 。V = 成功完成任務。

結束語

擬議的 Marco 框架為實時硬件設計任務求解提供了更靈活、更領域更專業的方法。通過使用任務圖形、靈活的單 AI 和多 AI 代理配置以及特定領域的工具和知識,我們為單元布局優化、Verilog 語法錯誤修復、Verilog 和 DRC 代碼生成以及問題塊、網絡和線纜的定時調試等任務開發了各種代理。

實驗結果表明,在芯片設計中使用基于 LLM 的協作式智能體可獲得驚人的性能和效率優勢。

硬件設計智能體研究的未來方向包括:

- 使用高質量的硬件設計數據訓練 LLMs

- 提升基于 LLM 的智能體的硬件信號和波形調試能力

- 將 PPA 指標納入設計流程

- 為 LLM 代理開發更高效的自學習技術和內存系統,以解決更復雜的硬件任務

有關電子設計自動化的更多論文和項目,請參閱 NVIDIA Design Automation Research Group 頁面。

如果您對本文中重點介紹的技術感興趣,以下是相關論文列表:

- RTLFixer:使用大語言模型自動修復 RTL 語法錯誤 /NVlabs/RTLFixer GitHub repo

- VerilogCoder:采用基于圖形的規劃和基于抽象語法樹(AST)的波形追蹤工具的自主 Verilog 編碼代理 /NVlabs/VerilogCoder GitHub repo

- DRC-Coder:使用 LLM 自主代理自動生成 DRC 檢查器代碼

- 用于優化標準單元布局設計的大語言模型(LLM)