從智能文本生成大語言模型(LLMs)到創意圖像和視頻生成模型,生成式模型在過去幾年中掀起了巨大的浪潮。在 NVIDIA,我們正在探索使用生成式 AI 模型來加速電路設計流程,并提供更好的設計,以滿足對計算能力不斷增長的需求。

電路設計是一個具有挑戰性的優化問題。設計師通常需要平衡功率和面積等多個相互沖突的目標,并滿足特定時間等約束條件。設計空間通常是組合的,因此很難找到最優設計。之前對前綴電路設計的研究使用手工制作的啟發式和強化學習來探索廣闊的設計空間。有關更多詳細信息,請參閱《Towards Optimal Performance-Area Trade-Off in Adders by Synthesis of Parallel Prefix Structures and Cross-Layer Optimization for High Speed Adders: A Pareto Driven Machine Learning Approach》。

雖然這些方法有助于克服龐大的搜索空間,但它們與訓練的高計算成本有關,并且通常難以泛化。

我們的論文 CircuitVAE:Efficient and Scalable Latent Circuit Optimization(最近在設計自動化大會上發表),揭示了生成模型在電路設計中的潛力。我們證明,變分自動編碼器(VAEs),一類生成模型,可以生成更好的前綴加法器設計,而所需的計算成本遠低于之前方法所需的成本。

電路設計的復雜性

前綴加法器的設計空間非常龐大:大約有 tg? 可能設計用于添加兩個 n 位數,因此這確實是一項針對干草堆式挑戰。電路由邏輯門(例如 AND、OR 和 XOR)組成。連接它們以實現相同功能的方法有很多,但不同的連接會改變電路的觀察功率、性能和面積。

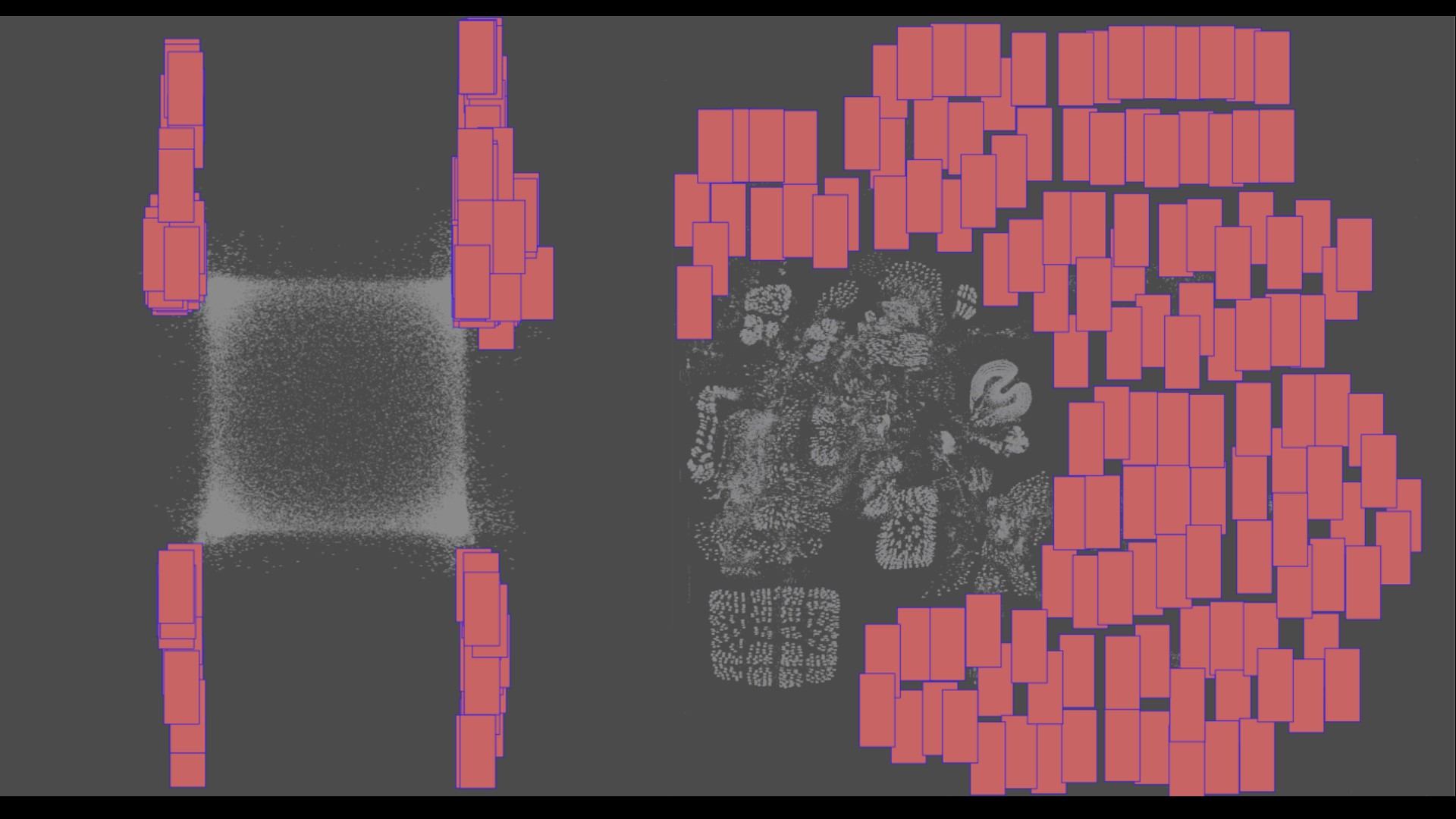

在我們的論文中,我們重點討論了優化前綴加法器,這是現代 GPUs 中常見的一類電路。如圖 1 所示,我們用樹表示前綴加法器。我們將面積和延遲這兩個指標最小化,并使用加權和將其合并為單個目標。

什么是變分自編碼器?

VAEs 是估計一些數據分布的生成模型。訓練一個 VAE 模型后,我們可以從估計的分布中進行采樣。VAEs 可用于對從圖像到圖形等不同模式的數據建模。一個 VAE 模型由編碼器和解碼器組成。

在圖像生成時,編碼器會將輸入圖像映射到稱為 latent space 的向量分布。解碼器會將編碼圖像的向量轉換回圖像。VAE 的訓練方法是最大限度地減少輸入和輸出之間的重建損失,以及 latent space 的正則化損失。VAE 是生成模型,因為它們可以通過從 latent space 采樣向量并使用習得的解碼器對其進行解碼來生成新的輸出。

電路 VAE:用于電路設計的 VAE

CircuitVAE 是一種搜索算法,可在連續空間中嵌入計算圖形,并通過梯度下降優化學習的物理模擬代理。它學習將電路嵌入連續隱空間,并根據隱表示預測質量指標(例如面積和延遲)。當使用神經網絡進行實例化時,成本預測器是完全可微的。因此,可以在隱空間中應用梯度下降來優化電路指標,從而規避在組合設計空間中搜索的挑戰。

電路 VAE 訓練

CircuitVAE 訓練損失分為兩部分:

- 標準 VAE 重建和正則化損失。

- 真值和預測區域之間的均方誤差,以及使用編碼電路隱向量的成本預測器模型產生的延遲。

在擬合成本預測器的同時,隱性空間根據成本進行組織,這適用于基于梯度的優化。一組加法器通過遺傳算法生成,以引導訓練。還可以使用隨機樣本的加法器開始。

基于梯度的優化

在訓練 CircuitVAE 模型后,該模型將用于尋找可最大限度降低成本的前綴樹結構。首先,使用成本加權采樣技術選擇 latent vector,這種技術可確保從良好的設計開始。然后,通過最大限度地減少成本預測器模型估計的成本,對該向量進行梯度下降修改。最終,latent vector 被解碼為前綴樹并進行合成,以獲得其實際成本。

迭代

完整的 CircuitVAE 算法交織在訓練和優化階段。在每一輪模型訓練后,都會通過基于梯度的優化和物理合成來收集更多數據。模型擬合會隨著不斷增長的電路和相關指標數據集恢復,從而導致成本預測器模型的準確性提高,形成良性循環,實現更有針對性的優化。

結果

我們測試了具有 32 個輸入和 64 個輸入(前綴樹電路的寬度,分別對應 32 位和 64 位)的電路設計方法。為了為我們的物理合成提供模擬所需的組件,我們使用了名為 Nangate45 的開源單元庫。

圖 4 顯示了成本進度,而每種方法都通過物理模擬評估更多設計。與基準方法相比,CircuitVAE 始終實現最低的成本。RL 和 GA 在離散域中進行優化,探索速度緩慢,而 CircuitVAE 的速度要快 2-3 倍,這要歸功于隱空間中基于梯度的優化。

我們使用專有單元庫評估了CircuitVAE在現實世界的前綴加法器任務中的表現,該單元庫使用從完整數據路徑中捕獲的輸入-輸出定時。圖5顯示,CircuitVAE生成的設計能夠形成比商業工具更好的Pareto前沿邊界和延遲。

結束語

CircuitVAE 展示了生成模型在電路設計任務中的強大功能。在潛在空間(而不是電路設計的組合式大型離散空間)中運行,可以通過降低計算成本的形式獲得持續優化的好處。我們認為,從離散到連續的這種轉換在硬件設計的其他領域(例如位置和路線)中具有前景。我們預計,生成模型將在硬件設計中發揮越來越重要的作用。

有關 CircuitVAE 的更多信息,請參閱 CircuitVAE:高效且可擴展的潛在電路優化。

?